# Documentation and LLCUs

# Documentation/Wiki

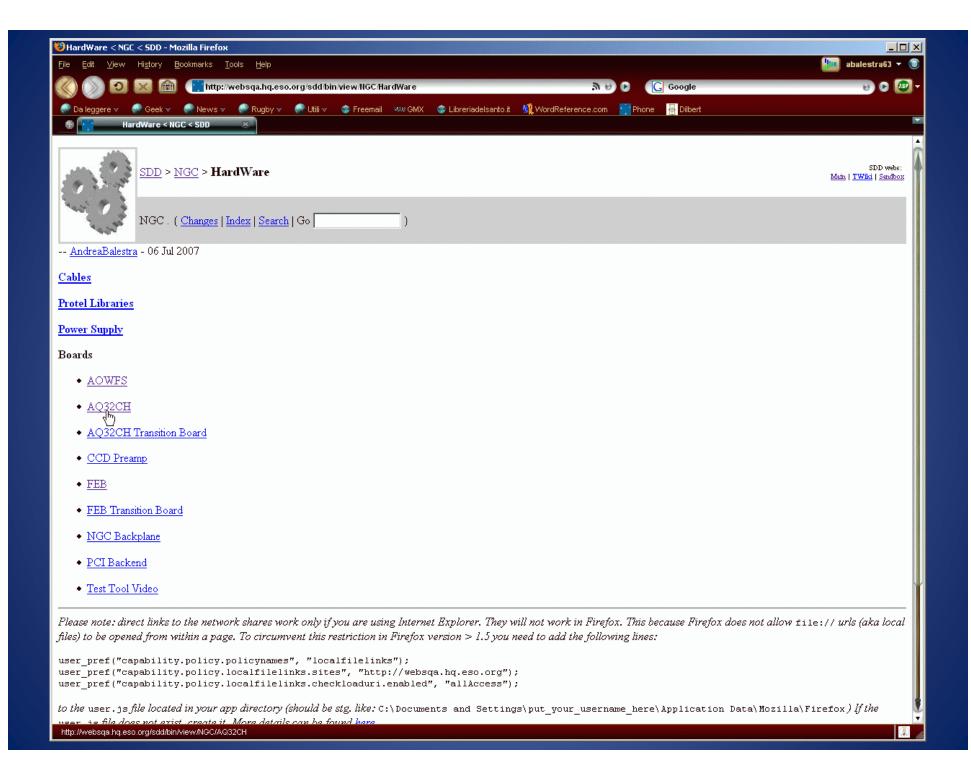

- Wiki contains (almost) everything and allows interaction with the content Among others you can find here:

- All documents (user, design...)

- Production manual

- Boards' history files and bug reports

- Link to shared drive containing all schematics

- Currently it is hosted by SDD wiki (TWiki), waiting for IT decision on a more suitable place

- Access is restricted

- ▶ If you feel you need access to it send an email to ngc@eso.org

#### KMOS final NGC-system, which is estimated to be delivered on APRIL 2008, contains the following modules:

| Module name        | Serial number               | Revision | Location     |  |

|--------------------|-----------------------------|----------|--------------|--|

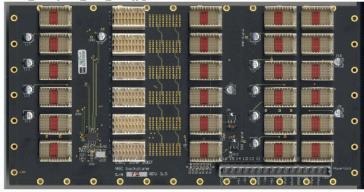

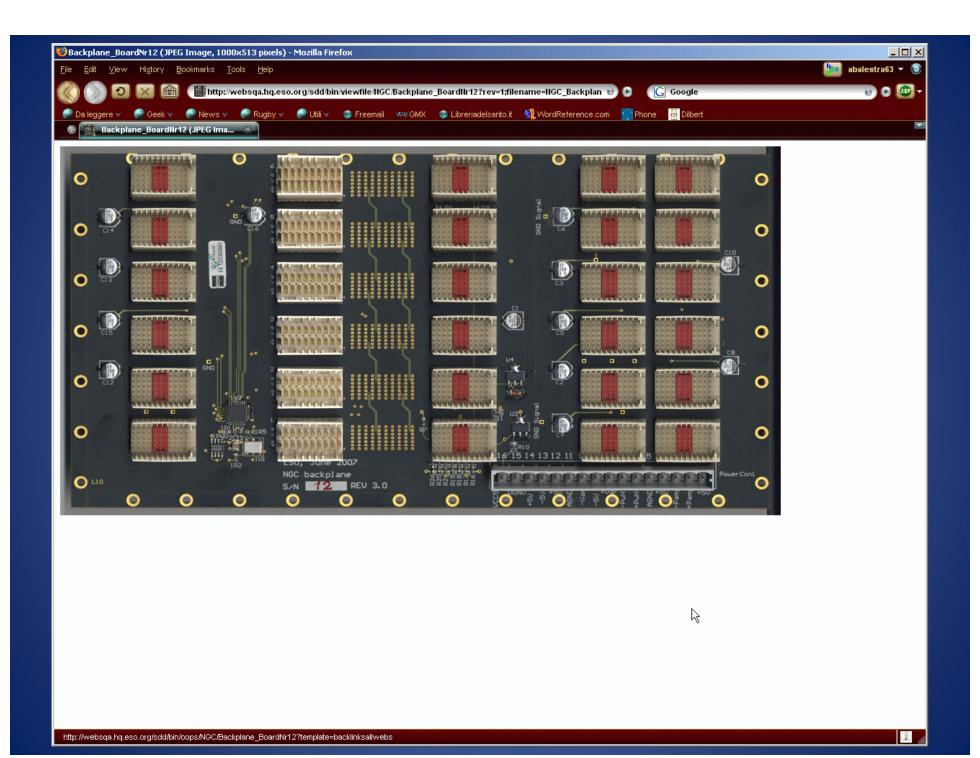

| Backplane          | Backplane SN 12             | 3        | ESO-Garching |  |

| Front End Basic    | FEB 51 12                   | 4        | ESO-Garching |  |

| FEB Transition     | FEB Trans 11                | 3        | ESO-Garching |  |

| AQ-32CH            | AQ-32 SN 10                 | 3        | ESO-Garching |  |

| AQ-32CH            | <u>AQ-32 SN 11</u>          | 3        | ESO-Garching |  |

| AQ-32CH            | <u>AQ-32 SN 15</u>          | 3        | ESO-Garching |  |

| AQ-32CH Transition | AQ-32 Trans 12 <u>?</u>     | 3        | ESO-Garching |  |

| AQ-32CH Transition | AQ-32 Trans 13 <sup>?</sup> | 3        | ESO-Garching |  |

| AQ-32CH Transition | AQ-32 Trans 14 <sup>?</sup> | 3        | ESO-Garching |  |

Topic KMOS . { Edit | Attach | Backlinks: Web All webs | Printable | History: r3 \le r2 \le r1 More }

Parents: WebHome > NgcSystems

TWiki Copyright @ by the contributing authors. All material on this collaboration platform is the property of the contributing authors. Ideas, requests, problems regarding SDD? Send feedback

#### board SN: #12

#### The following changes have been done:

- C2 has been replaced by a 3.3V zener diode.

- NGC\_Backplane\_rev3\_12B.jpg:

| <u>Attachment</u> ♦         | Action | Size    | Date                | Who                   | Comment |

|-----------------------------|--------|---------|---------------------|-----------------------|---------|

| NGC Backplane rev3, 12B.jpg | manage | 142.0 K | 27 Sep 2007 - 11:50 | <u>LeanderMehrgan</u> |         |

| d <sub>III</sub>            |        |         |                     |                       |         |

Topic Backplane\_BoardNr12 . { Edit | Attach | Backlinks: Web All webs | Printable | History: r1 More }

Parents: WebHome > HardWare > NGCBackplane > History Backplane

TWIKI Copyright © by the contributing authors. All material on this collaboration platform is the property of the contributing authors. Ideas, requests, problems regarding SDD? Send feedback

#### AQ32 Rev.3.0 BUGS

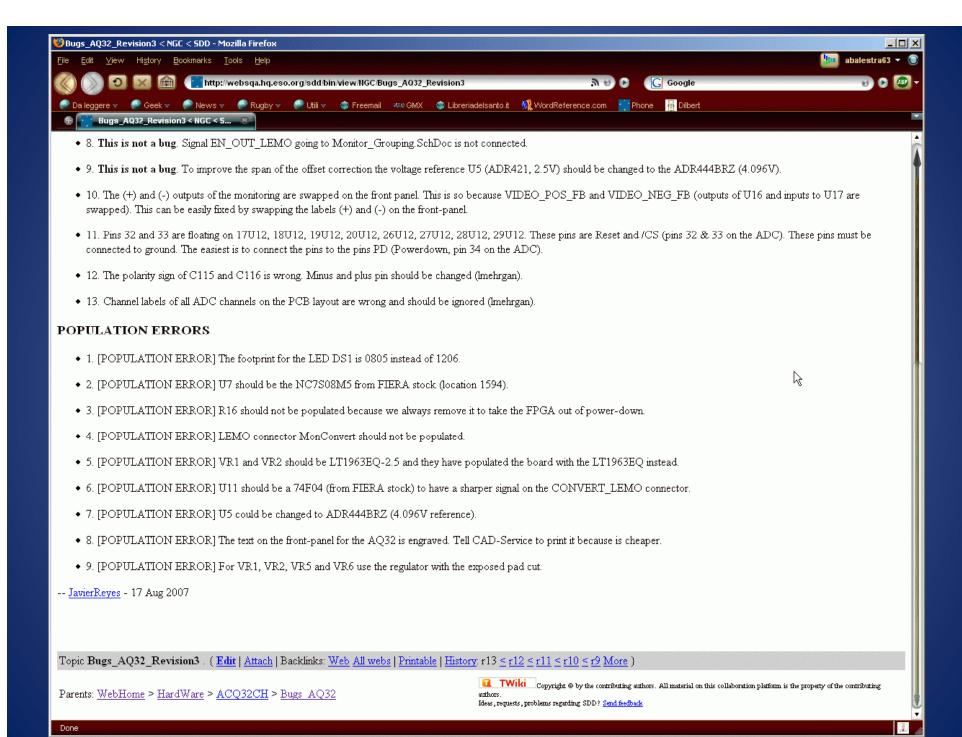

- 1. The footprint for U15 (the offset DAC LT1206) is a little bit too big. It must be a 16-Lead Plastic SSOP (Narrow .150 Inch).

- 2. The exposed pad for the big voltage regulator is wrong (VR6, VR1, VR2 and VR5)

- 3. On LED DS1, it is better to have the LED always on after DONE-DUT. For that use a Tiny-Logic AND-gate instead of an NAND-gate.

- 4. The resistors R5, R20 and R21 must right after U2 and before S16 and SJ7. When the jumpers SJ6 and SJ7 are open SYS\_CLK comes from the backplane and these resistors attenuate too much the signal. However, when the board is tested in standalone, the resistor are needed so U2 generates the clock.

- 5. Signals CONVERT\_TO\_BP, CONVERT\_TO\_BP#, CONVERT1\_TO\_BP and CONVERT1\_TO\_BP# are not connected to connected J3. I have temporarily connected CV1 and CV1# to pins B22, C22 respectively (GPIO3, GPIO4) on the FPGA.

- 6. Signals CONVERT1\_TO\_BP and CONVERT1\_TO\_BP# are not connected to connected J3. They are floating and that's the reason why the LED Busy on the front-panel is always on.

- 7. This is not a bug. Change U11. From 74ALS04 to 74F04 (cleaner convert signal on the oscilloscope)

- . 8. This is not a bug. Signal EN OUT LEMO going to Monitor Grouping SchDoc is not connected.

- 9. This is not a bug. To improve the span of the offset correction the voltage reference U5 (ADR421, 2.5V) should be changed to the ADR444BRZ (4.096V).

- 10. The (+) and (-) outputs of the monitoring are swapped on the front panel. This is so because VIDEO\_POS\_FB and VIDEO\_NEG\_FB (outputs of U16 and inputs to U17 are swapped). This can be easily fixed by swapping the labels (+) and (-) on the front-panel.

- 11. Pins 32 and 33 are floating on 17U12, 18U12, 19U12, 20U12, 26U12, 27U12, 28U12, 29U12. These pins are Reset and /CS (pins 32 & 33 on the ADC). These pins must be connected to ground. The easiest is to connect the pins to the pins PD (Powerdown, pin 34 on the ADC).

- 12. The polarity sign of C115 and C116 is wrong. Minus and plus pin should be changed (Imehrgan).

- 13. Channel labels of all ADC channels on the PCB layout are wrong and should be ignored (Imehrgan).

#### POPULATION ERRORS

• 1 [POPIT.ATTON ERROR] The footprint for the LED DS1 is 0805 instead of 1206

1/2

# Documentation/web

- Web (http://www.eso.org/projects/ngc) contains all public documents

- It is not foreseen as a maintenance tool, but as a mean to inform about NGC

## NGC LLCUs (Linux Local Control Units)

- LLCUs are standard Linux machines as defined by SDD in: http://websqa.hq.eso.org/sdd/bin/view/SDDInfo/LinuxStandardHw

- NGC team takes care of verifying upfront that the standard models covers minimum NGC requirements:

- 2 x 3.00GHz CPU (4 MB cache) for real parallel processing

- 2GB Memory

- 2 Full-width PCI slots (64 Bit 66 Mhz)

- Gigabit Ethernet

- Graphic Card for maintenance operations. No special requirement.

- Hard Disk >160 GB, i.e. capable of some local storage for testing purposes (given an upper limit of occupation of operating system + VLTSW of 10 GB).

- Rack mountable

- Dimension compatible with rack requirements as defined by TEC.

- Safe under the applicable earthquake conditions

### **LLCUs** location

- It is technically possible to have the LLCUs either close to the instrument (e.g. Nasmyth platform) or in the Computer Room.

- CRE N. VLT-CRE-ESO-13660-4412 (asking for a formal acceptance of LLCUs in Computer Room was rejected but somehow accepted (!):

- Rejected as CRE

- Accepted the concept: each project can ask for relocation of LLCU(s) in the Computer Room